|

| |

| |

|

Last updated:

21-09-09 |

|

|

|

|

| |

| Try one (or

better all three) version of the 8-bit counter found

below

The purpose to demonstrate the difference between

CLEAR and RESET |

| One of the three

versions below will not produce the correct

functionality (my intention :) which one?

|

| Be course the

Clock signal should be <Btn0> at kit - must you

"persuade" the ISE software to accept this

By the warning can you see that done with a protest

as well :-)

|

|

| |

| |

|

|

| |

| Design #1 |

|

| |

| |

|

|

|

|

| Design #2 |

|

| |

| |

|

|

|

|

|

|

| |

Content of the

User Constrain File

|

|

|

| |

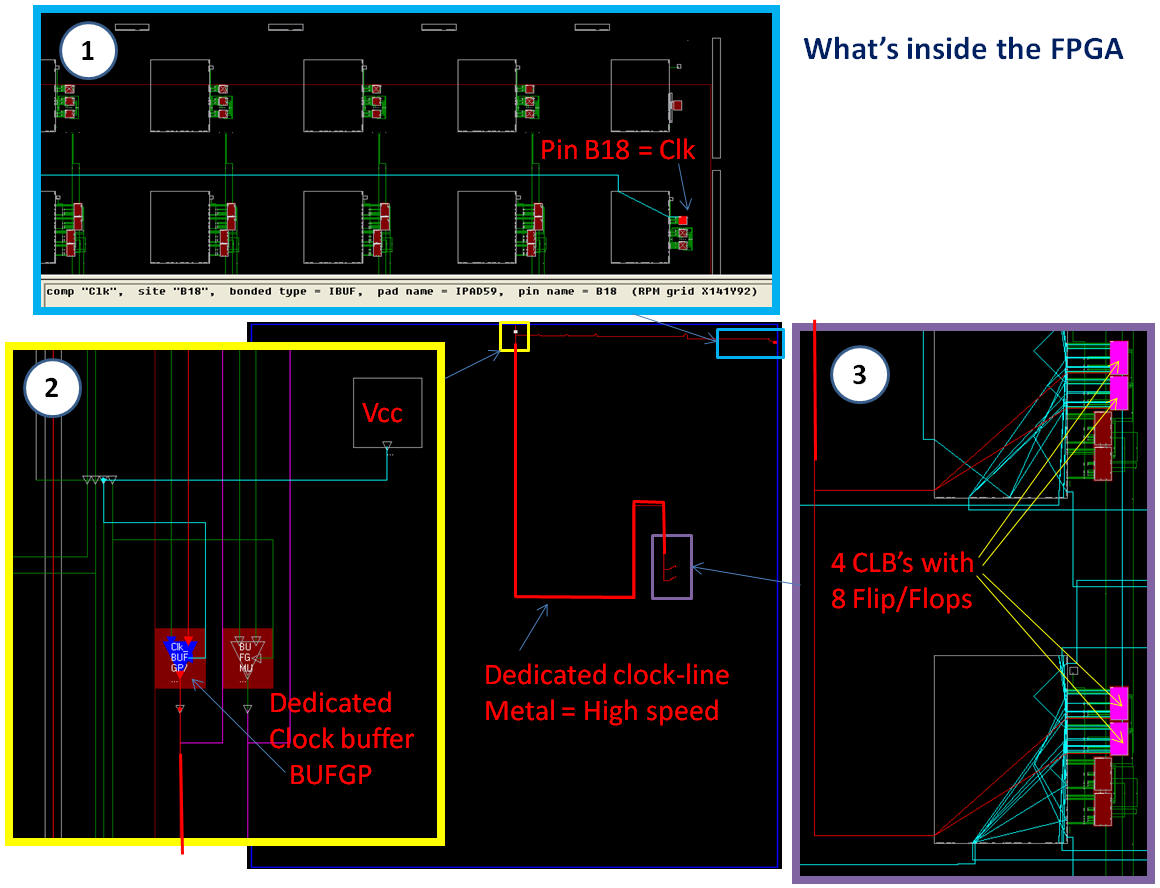

Read more about

BUFG/BUFGP in the documentations of the Spartan 3E family

|

| |

In order to

provide fast propagation of the clock-signals inside

the FPGA will have special fast connection-lines

(Clock highways)

The BUFG / BUFGP could be one way to enter such a

line. Another way could be to use one of the

dedicated Clock pins like B8.

|

| |

|

|

|

|

|

|

|