Data types, Operators and

Attributes

|

| |

Topics: |

Last updated:

06-08-09 |

| |

| Chapter 3 of Pedroni gives a

nearly complete overview of the Data types and operators of

VHDL. Its important to know this as VHDL a very strongly typed

language. However can most task and designs be solved with a few

data types.

|

| If you decide to use the type

Bit

and Bit_vector

will the synthesize tool properly accept this. But if you want

to simulate (and believe me - you will) are you bound for

problems as the simulation tool prefers

Std_logic

instead of Bit.

|

|

|

Std_logic |

Will cover 9

different values where: '1', '0' and 'Z' are the most useful |

|

Std_logic_vector |

The bus version of this

type can have indexes like (1 to

4) or (7 downto 0) |

|

Integer |

Refers to a 32-bit value -

in order to reduce the number of bit use:

range x to y |

|

Enumerated |

Will be useful in concern

with State Machines |

|

Boolean |

Can be useful in "more

advanced" designs |

|

Time |

Will be useful in Test

Benches |

|

Array |

Can be useful in order to

define RAM / ROM structures - however will this type seldom give you

the optimal utilization of the FPGA |

| |

|

|

Sig'Event |

Will properly be the most

useful of the attributes - but it depends on your ambitions |

|

Rising_edge(sig) |

This function will

replace: Sig'Event and Sig='1' |

|

Falling_edge(sig) |

This function will

replace: Sig'Event and Sig='0' |

| |

|

|

Operators |

Your allowed to use

all common operators like: + - * / and

or etc. But the division will

give you problems for synthesizing. |

|

& |

The Concatenation

operator will be very useful when it comes to mixing busses and

signals to new busses |

| |

|

|

|

| |

|

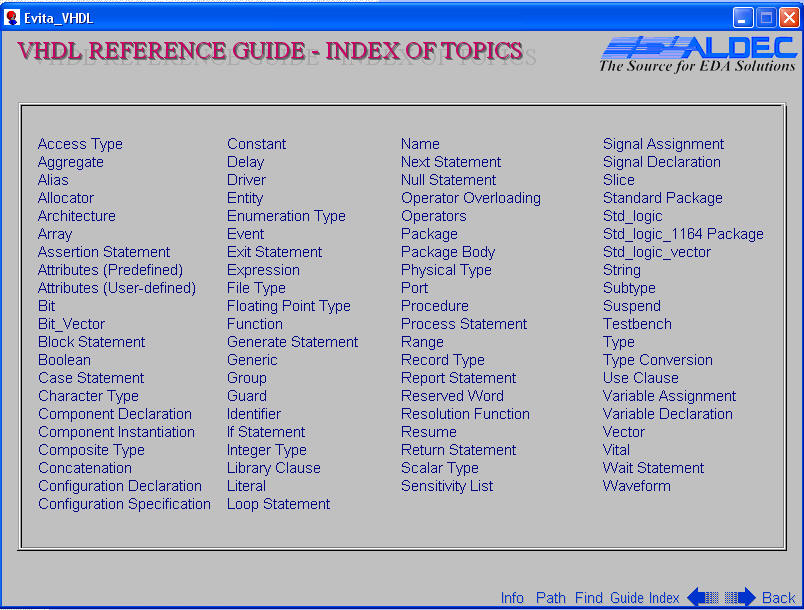

Search the net for EVITA VHDL - an interactive book

on VHDL from Aldec - can be downloaded for free.

|

| |

|

| |

|

|

| |

|

Conversions functions in VHDL -

can be found in Language Assist of ISE |

The most important will properly be:

CONV_STD_LOGIC_VECTOR( , )

and CONV_INTEGER(

)

|

|

|

|