|

|

|

|

|

|

|

Carry

Lookahead Addition (Trade Area to gain Speed) |

|

|

|

In order to

quit the "slow" ripple carry chain will be necessary

to use logic which predict the carry for each stage

instead of waiting for the carry to propagate

through the chain.

Each two bit pairs can either

Generate or Propagate a Carry.

The Carry Generator can be formed with an And gate

(or less ???)

The Carry Propagation will cost a Xor-gate.

By nature will it cost more

and more logic to "foresee" the Carry when moving

toward more significant bits.

|

|

|

|

|

The gate-cost for a N-bit "Look Ahead" carry-chain will

be |

|

|

Hence a 32-bit adder will use 624 gates, but for this

price will the propagation delay be only 4 x Tpgate

Note! however that some gates with up to 32 input. |

|

|

|

|

|

|

|

|

|

|

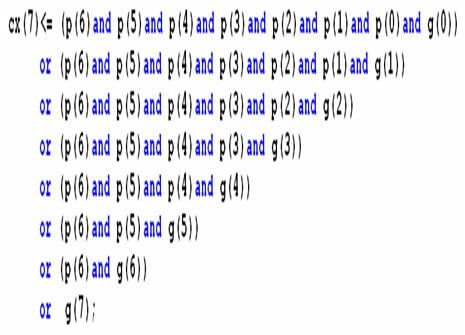

Extract from the solution below.Please note

generate statements which produces all the Propagate

and Generate components.

|

|

|

|

|

|

|

|

A "Lazy" hardware designer

would properly prefer using the time to figure out

code which could do job automatically.

The process at the left seems

to work ok and generates code for a 8-bit adder.

Its easy to modify to a

32-bit adder as well and in fact I tried as well.

Just to see the hardware cost (should be huge in

FPGA) and try a simulation.

But I learned something

about HDL, synthesise tool and FPGA structures as

well.

|

|

|

|

|

This was the Hardware cost for

a 32-bit Ripple Carry Adder.

|

|

|

|

|

This is the Hardware cost for

a 32-bit Carry Lookahead Adder.

Hard to find the difference

and the simulation also shows that no matter how I

try to describe the Hardware Structure will the

synthesise tool recognize an adder but it refuses to

implement it.

Exercise: Try to implement

a 8-bit Carry Lookahead Adder with a Schematic

Diagram.

|

|

|

|

|

|

|