In order to convert

digital values (n-bit vectors etc) to the equivalent analogue

value (for instance 0 to 5 volt) can it be necessary connect

hardware DAC to the system. Those usually based on a 2R-ladder

network and will be quite expensive when a higher resolution

needed (12-bit or more).

A cheaper alternative

could a Pulse Modulation based DAC - like the PWM and

Sigma-Delta types.

Lots of documentation can

be found on the net - concerning the theories behind and the

frequency spectres etc. The exercises below mostly about the

VHDL implementations of a PWM and a PPM Sigma-Delta conversion.

|

| |

|

|

|

| |

You may adjust the Clk-frequency

between 25, 50 and 100 MHz in order to observe the PWM

and PPM outputs.

SW6..SW0 = the 7- bit PCM value for the PWM and PPM

duty cycles.

SW7

= Selection between High and Low Clk frequency -

Calculate the exact number yourself

LD3

= The PWM output

LD4

= The PPM output |

| |

|

| |

|

|

|

Block

diagram for a PWM Digital to Analogue Converter |

|

The PWM generator basically a Counter and a Comparator.

If the Max counter value a power of 2 minus 1(like 127, 255 etc)

will this circuit normally work alright.

If the Max counter value below will there be a chance

(read - risk) of mal-functionality due to the fact that not all bit changes

simultaneously - Consider an extra register between the counter and the

comparator.

|

|

|

|

Block

diagram for a Sigma-Delta PPM Digital to Analogue Converter |

|

The PPM signal will have a

"more equal" contribution compared with the similar

PWM solution.Hence

will the requirements for filtering be less compared

with the similar PWM solution.

In case of power output

will the power-lost be equal to the number of

switches (on/off and off/on)

|

|

|

|

|

| |

|

Please note!

In order to avoid clock-skew are all F/F's driven by

the same Clk-signal.The

Scaled_Clk will only be high for one Clk-period and

hence can it serve as CE (Clock Enable) signal in

the processes for PWM and PPM generation.

|

|

| |

|

|

|

|

| |

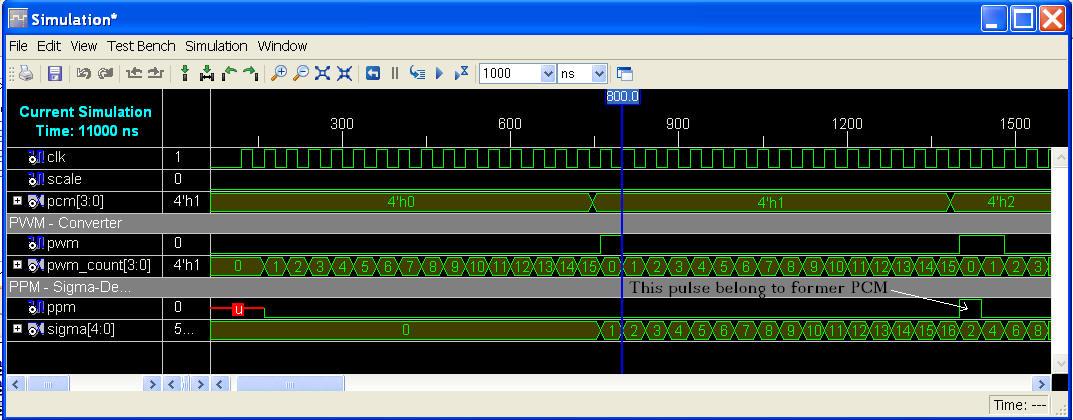

Simulation with

N=4

and Max=16

|

| |

Please note - The circuit above only a

suggestion which not optimized for size/speed.

It appears that the PPM value first will be 1 after

16 clock-pulses - this fact shouldn't be a problem

in real-life applications, but its possible fix "the

bug" with minor changes (how?)

|

| |

|

| |

|

| |

|

| |

|

| |

|

| |

|

| |

|

| |

|

| |

|

| |

|

| |

|

| |

|

| |

|

| |

|

| |

|

|

|

|

|

|

|

|